MPC5565RM Rev. 1.1, 05/2012

# MPC5565 Microcontroller Reference Manual

This MPC5565 Reference Manual set consists of the following files:

- MPC5565 Reference Manual Addendum, Rev 1

- MPC5565 Microcontroller Reference Manual, Rev 2

### Freescale Semiconductor Reference Manual Addendum

MPC5565RMAD Rev. 2, 05/2012

# MPC5565 Reference Manual Addendum

This errata document describes corrections to the *MPC5565 Preliminary Microcontroller Reference Manual*, order number MPC5565RM. For convenience, the addenda items are grouped by revision. Please check our website at <a href="http://www.freescale.com/powerarchitecture">http://www.freescale.com/powerarchitecture</a> for the latest updates.

The current version available of the *MPC5565 Microcontroller Reference Manual* is Revision 1.0.

#### **Table of Contents**

|   | Addendum for Revision 1.0 | 2  |

|---|---------------------------|----|

| 2 | Revision history 1        | 15 |

### 1 Addendum for Revision 1.0

Table 1. MPC5565RM Rev 1.0 addendum

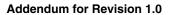

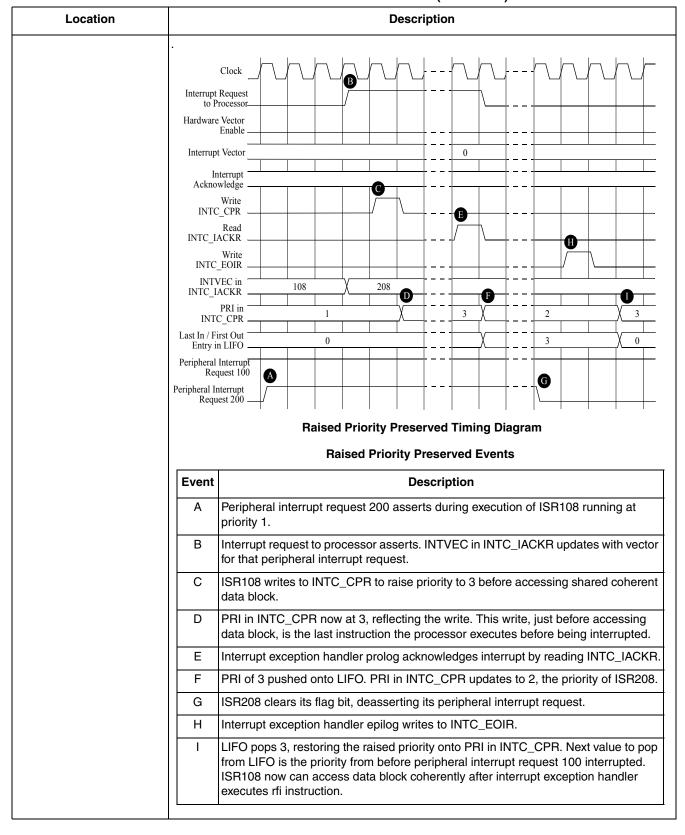

| Location                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description                            |                                                                                                                                                                                       |     |      |                                                         |        |                                                                                                                     |         |                          |                               |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------|---------|--------------------------|-------------------------------|--|

| Section 12.4.2.7/Page 12-42                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        | Change sentence "The bytes indicated as '—' are not driven during that write cycle" to read "The bytes indicated as '—' are indeterminate and may be driven during that write cycle." |     |      |                                                         |        |                                                                                                                     |         |                          |                               |  |

| Table 12-19, "Data Bus<br>Contents for Write<br>Cycles"/Page 12-43                                                                                                                                                                                                                                                                                                                                                                                               |                                        |                                                                                                                                                                                       |     |      |                                                         |        |                                                                                                                     |         |                          | ts for write c<br>"D0:D7" and |  |

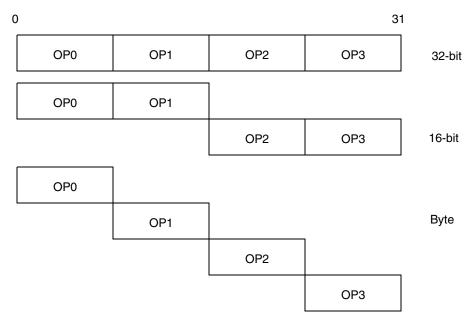

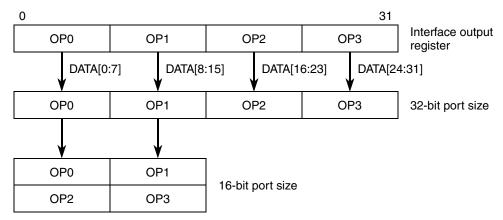

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Transfer                               | TSIZ                                                                                                                                                                                  | Add | ress |                                                         | 32-Bit | Port Size                                                                                                           |         | 16-Bit                   | Port Size <sup>1</sup>        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Size                                   | [0:1]                                                                                                                                                                                 | A30 | A31  | D0:D7                                                   | D8:D15 | D16:D23                                                                                                             | D24:D31 | D0:D7                    | D8:D15                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Byte                                   | 01                                                                                                                                                                                    | 0   | 0    | OP0                                                     | _      | _                                                                                                                   | _       | OP0                      | _                             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        | 01                                                                                                                                                                                    | 0   | 1    | _                                                       | OP1    | _                                                                                                                   | _       | _                        | OP1                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        | 01                                                                                                                                                                                    | 1   | 0    | _                                                       | _      | OP2                                                                                                                 | _       | OP2                      | _                             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        | 01                                                                                                                                                                                    | 1   | 1    | _                                                       | _      | _                                                                                                                   | OP3     | _                        | OP3                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16-bit                                 | 10                                                                                                                                                                                    | 0   | 0    | OP0                                                     | OP1    | _                                                                                                                   | _       | OP0                      | OP1                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        | 10                                                                                                                                                                                    | 1   | 0    | _                                                       | _      | OP2                                                                                                                 | OP3     | OP2                      | OP3                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32-bit                                 | 00                                                                                                                                                                                    | 0   | 0    | OP0                                                     | OP1    | OP2                                                                                                                 | OP3     | OP0/<br>OP2 <sup>2</sup> | OP1/OP3                       |  |

| NOTES:  Also applies when DBM=1 for 16-bit data bus mode.  This case consists of two 16-bit external transactions, the first writing OP0 and the second writing OP2 and OP3.  Table 9-23, "DMA Request Summary for eDMA"/Page 9-39  Change one row in the table to correct information about eSCI COMBTX DMA request Summary for eDMA"/Page 17-cansmit Data Register Empty and LIN Transmit Data Ready flags drive the DMA 17-cansmit Complete flag is not used. |                                        |                                                                                                                                                                                       |     |      |                                                         |        | request. Or                                                                                                         |         |                          |                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DMA Request Channel Source Description |                                                                                                                                                                                       |     |      |                                                         | 1      |                                                                                                                     |         |                          |                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | eSCIA_COMBTX                           |                                                                                                                                                                                       | 18  |      | ESCIA.SR[TDRE] II<br>ESCIA.SR[TC] II<br>ESCIA.SR[TXRDY] |        | eSCIA combined DMA<br>request of the Transmit<br>Data Register Empty<br>and LIN Transmit Data<br>Ready DMA requests |         | ansmit<br>mpty<br>t Data |                               |  |

Table 1. MPC5565RM Rev 1.0 addendum (continued)

| Location                                                         | Description                                                 |                  |                |                                                       |                     |  |

|------------------------------------------------------------------|-------------------------------------------------------------|------------------|----------------|-------------------------------------------------------|---------------------|--|

| Table 10-9, "MPC5565<br>Interrupt Request<br>Sources"/Page 10-19 | Change three rows in the not assigned to the con            |                  |                | mation. The three interrupt                           | requests were       |  |

|                                                                  | Hardware Vector<br>Mode Offset                              | Vector<br>Number | Source         | Description                                           |                     |  |

|                                                                  | 0x0850                                                      | 133              | DSPI_BSR[TFFF] | DSPI B transfer FIFO fill f                           | lag                 |  |

|                                                                  | 0x0860                                                      | 134              | DSPI_BSR[TCF]  | DSPI B transfer complete                              | flag                |  |

|                                                                  | 0x0870                                                      | 135              | DSPI_BSR[RFDF] | DSPI B receive FIFO drai                              | n flag              |  |

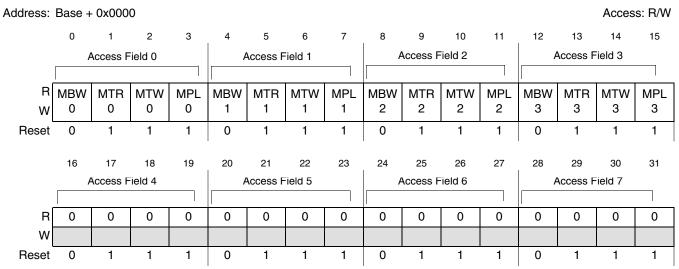

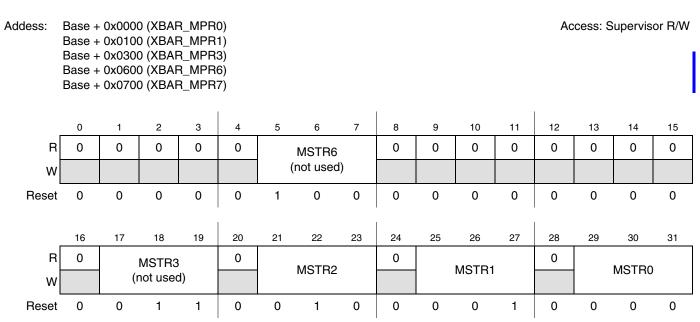

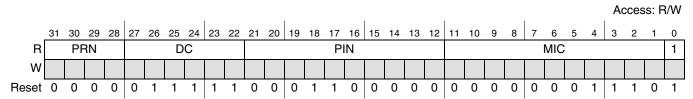

| Figure 5-2, "Master Privilege<br>Control Registers"/Page 5-5     | Change read status for  16 17 18  Access  R  W  Reset 0 1 1 | 19 20            |                | 25 26 27 28 29 3<br>Access Field 6 Acces              | 30 31<br>ss Field 7 |  |

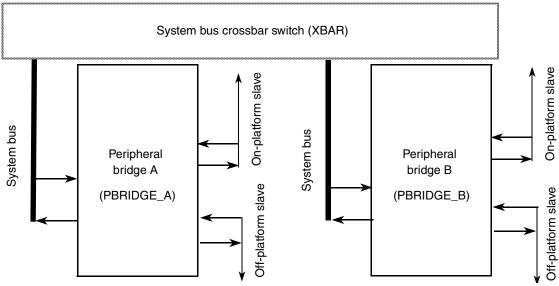

| Table A-1, "Module Base<br>Addresses"/Page A-1                   |                                                             |                  |                | g underscore (PBRIDGEA<br>nly two rows of the table a |                     |  |

|                                                                  |                                                             | Module           |                | Base Address                                          | Page                |  |

|                                                                  | Peripheral Bridge A (F                                      | BRIDGE_          | A)             | 0xC3F0_0000                                           | Page A-2            |  |

| 1                                                                | Peripheral Bridge B (F                                      | BBIDGE           | R)             | 0xFFF0_0000                                           | Page A-31           |  |

Table 1. MPC5565RM Rev 1.0 addendum (continued)

| Location                                                  | Description                                                                                                   |                  |              |                                 |  |  |  |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------|--------------|---------------------------------|--|--|--|--|--|

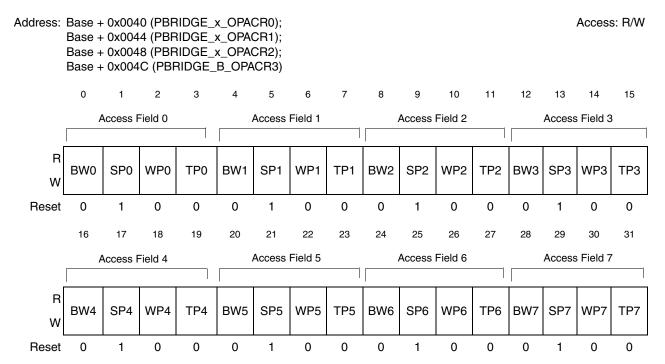

| Table A-2, "MPC5565<br>Detailed Register<br>Map"/Page A-2 | Correct names of peripheral bridge A control registers by adding underscore (PBRIDGEA_x becomes PBRIDGE_A_x). |                  |              |                                 |  |  |  |  |  |

|                                                           | Register Description                                                                                          | Register Name    | Used<br>Size | Address                         |  |  |  |  |  |

|                                                           | Peripheral bridge A master privilege control register                                                         | PBRIDGE_A_MPCR   | 32-bit       | Base + 0x0000                   |  |  |  |  |  |

|                                                           | Reserved                                                                                                      | _                | _            | Base + (0x0004-0x001F)          |  |  |  |  |  |

|                                                           | Peripheral bridge A peripheral access control register 0                                                      | PBRIDGE_A_PACR0  | 32-bit       | Base + 0x0020                   |  |  |  |  |  |

|                                                           | Reserved                                                                                                      | _                |              | Base + (0x0024-0x003F)          |  |  |  |  |  |

|                                                           | Peripheral bridge A off-platform peripheral access control register 0                                         | PBRIDGE_A_OPACR0 | 32-bit       | Base + 0x0040                   |  |  |  |  |  |

|                                                           | Peripheral bridge A off-platform peripheral access control register 1                                         | PBRIDGE_A_OPACR1 | 32-bit       | Base + 0x0044                   |  |  |  |  |  |

|                                                           | Peripheral bridge A off-platform peripheral access control register 2                                         | PBRIDGE_A_OPACR2 | 32-bit       | Base + 0x0048                   |  |  |  |  |  |

|                                                           | Reserved                                                                                                      | _                |              | Base + (0x004C-<br>0xC3F7_FFFF) |  |  |  |  |  |

Table 1. MPC5565RM Rev 1.0 addendum (continued)

| Location                                                   | Description                                                                                                   |                  |         |                                  |  |  |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------|---------|----------------------------------|--|--|--|--|

| Table A-2, "MPC5565<br>Detailed Register<br>Map"/Page A-23 | Correct names of peripheral bridge B control registers by adding underscore (PBRIDGEB_x becomes PBRIDGE_B_x). |                  |         |                                  |  |  |  |  |

|                                                            | Register Description                                                                                          | Used<br>Size     | Address |                                  |  |  |  |  |

|                                                            | Peripheral bridge B master privilege control register                                                         | PBRIDGE_B_MPCR   | 32-bit  | Base + 0x0000                    |  |  |  |  |

|                                                            | Reserved                                                                                                      | _                |         | Base +<br>(0x0004-0x001F)        |  |  |  |  |

|                                                            | Peripheral bridge B peripheral access control register 0                                                      | PBRIDGE_B_PACR0  | 32-bit  | Base + 0x0020                    |  |  |  |  |

|                                                            | Reserved                                                                                                      | _                |         | Base + (0x0024-0x0027)           |  |  |  |  |

|                                                            | Peripheral bridge B peripheral access control register 2                                                      | PBRIDGE_B_PACR2  | 32-bit  | Base + 0x0028                    |  |  |  |  |

|                                                            | Reserved                                                                                                      | _                | _       | Base +<br>(0x002C-0x003F)        |  |  |  |  |

|                                                            | Peripheral bridge B off-platform peripheral access control register 0                                         | PBRIDGE_B_OPACR0 | 32-bit  | Base + 0x0040                    |  |  |  |  |

|                                                            | Peripheral bridge B off-platform peripheral access control register 1                                         | PBRIDGE_B_OPACR1 | 32-bit  | Base + 0x0044                    |  |  |  |  |

|                                                            | Peripheral bridge B off-platform peripheral access control register 2                                         | PBRIDGE_B_OPACR2 | 32-bit  | Base + 0x0048                    |  |  |  |  |

|                                                            | Peripheral bridge B off-platform peripheral access control register 3                                         | PBRIDGE_B_OPACR3 | 32-bit  | Base + 0x004C                    |  |  |  |  |

|                                                            | Reserved                                                                                                      | _                | _       | (Base + 0x0050)-<br>0xFFF0_3FFF) |  |  |  |  |

Table 1. MPC5565RM Rev 1.0 addendum (continued)

Table 1. MPC5565RM Rev 1.0 addendum (continued)

| Location               | Description                                                                            |             |       |             |  |  |  |  |  |

|------------------------|----------------------------------------------------------------------------------------|-------------|-------|-------------|--|--|--|--|--|

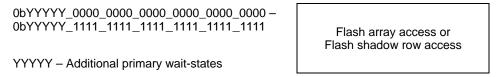

| Section13.3/ Page 13-4 | 4 Remove cross-reference to Table 13-2. Add the following table and update the cross-r |             |       |             |  |  |  |  |  |

|                        | Internal Flash External Emulation Mode                                                 |             |       |             |  |  |  |  |  |

|                        | Address                                                                                | Range       | YYYYY | Wait States |  |  |  |  |  |

|                        | 0x0000_0000                                                                            | 0x0000_0000 |       | 0           |  |  |  |  |  |

|                        | 0x0100_0000                                                                            | 0x012F_FFFF | 01000 | 8           |  |  |  |  |  |

|                        | 0x0200_0000                                                                            | 0x022F_FFFF | 10000 | 16          |  |  |  |  |  |

|                        | 0x0300_0000                                                                            | 0x032F_FFFF | 11000 | 24          |  |  |  |  |  |

|                        | 0x0400_0000                                                                            | 0x042F_FFFF | 00001 | 1           |  |  |  |  |  |

|                        | 0x0500_0000                                                                            | 0x052F_FFFF | 01001 | 9           |  |  |  |  |  |

|                        | 0x0600_0000                                                                            | 0x062F_FFFF | 10001 | 17          |  |  |  |  |  |

|                        | 0x0700_0000                                                                            | 0x072F_FFFF | 11001 | 25          |  |  |  |  |  |

|                        | 0x0800_0000                                                                            | 0x082F_FFFF | 00010 | 2           |  |  |  |  |  |

|                        | 0x0900_0000                                                                            | 0x092F_FFFF | 01010 | 10          |  |  |  |  |  |

|                        | 0x0A00_0000                                                                            | 0x0A2F_FFFF | 10010 | 18          |  |  |  |  |  |

|                        | 0x0B00_0000                                                                            | 0x0B2F_FFFF | 11010 | 26          |  |  |  |  |  |

|                        | 0x0C00_0000                                                                            | 0x0C2F_FFFF | 00011 | 3           |  |  |  |  |  |

|                        | 0x0D00_0000                                                                            | 0x0D2F_FFFF | 01011 | 11          |  |  |  |  |  |

|                        | 0x0E00_0000                                                                            | 0x0E2F_FFFF | 10011 | 19          |  |  |  |  |  |

|                        | 0x0F00_0000                                                                            | 0x0F2F_FFFF | 11011 | 27          |  |  |  |  |  |

|                        | 0x1000_0000                                                                            | 0x102F_FFFF | 00100 | 4           |  |  |  |  |  |

|                        | 0x1100_0000                                                                            | 0x112F_FFFF | 01100 | 12          |  |  |  |  |  |

|                        | 0x1200_0000                                                                            | 0x122F_FFFF | 10100 | 20          |  |  |  |  |  |

|                        | 0x1300_0000                                                                            | 0x132F_FFFF | 11100 | 28          |  |  |  |  |  |

|                        | 0x1400_0000                                                                            | 0x142F_FFFF | 00101 | 5           |  |  |  |  |  |

|                        | 0x1500_0000                                                                            | 0x152F_FFFF | 01101 | 13          |  |  |  |  |  |

|                        | 0x1600_0000                                                                            | 0x162F_FFFF | 10101 | 21          |  |  |  |  |  |

|                        | 0x1700_0000                                                                            | 0x172F_FFFF | 11101 | 29          |  |  |  |  |  |

|                        | 0x1800_0000                                                                            | 0x182F_FFFF | 00110 | 6           |  |  |  |  |  |

|                        | 0x1900_0000                                                                            | 0x192F_FFFF | 01110 | 14          |  |  |  |  |  |

|                        | 0x1A00_0000                                                                            | 0x1A2F_FFFF | 10110 | 22          |  |  |  |  |  |

|                        | 0x1B00_0000                                                                            | 0x1B2F_FFFF | 11110 | 30          |  |  |  |  |  |

|                        | 0x1C00_0000                                                                            | 0x1C2F_FFFF | 00111 | 7           |  |  |  |  |  |

|                        | 0x1D00_0000                                                                            | 0x1D2F_FFFF | 01111 | 15          |  |  |  |  |  |

|                        | 0x1E00_0000                                                                            | 0x1E2F_FFFF | 10111 | 23          |  |  |  |  |  |

|                        | 0x1F00_0000                                                                            | 0x1F2F_FFFF | 11111 | 31          |  |  |  |  |  |

|                        |                                                                                        |             |       |             |  |  |  |  |  |

| Location               | Description                                 |                             |                         |  |  |  |  |  |

|------------------------|---------------------------------------------|-----------------------------|-------------------------|--|--|--|--|--|

| Table 16-9/ Page 16-15 | Bit 7—DMA: Replace the tab following table. | ole that shows the eMIOS ch | annels that don't suppo |  |  |  |  |  |

|                        | eMIOS Cha                                   | nnel DMA = 0                | DMA = 1                 |  |  |  |  |  |

|                        | 0                                           | Interrupt                   | DMA request             |  |  |  |  |  |

|                        | 1                                           | Interrupt                   | DMA request             |  |  |  |  |  |

|                        | 2                                           | Interrupt                   | DMA request             |  |  |  |  |  |

|                        | 3                                           | Interrupt                   | DMA request             |  |  |  |  |  |

|                        | 4                                           | Interrupt                   | DMA request             |  |  |  |  |  |

|                        | 5                                           | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 6                                           | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 7                                           | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 8                                           | Interrupt                   | DMA request             |  |  |  |  |  |

|                        | 9                                           | Interrupt                   | DMA request             |  |  |  |  |  |

|                        | 10                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 11                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 12                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 13                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 14                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 15                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 16                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 17                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 18                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 19                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 20                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 21                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 22                                          | Interrupt                   | Reserved                |  |  |  |  |  |

|                        | 23                                          | Interrupt                   | Reserved                |  |  |  |  |  |

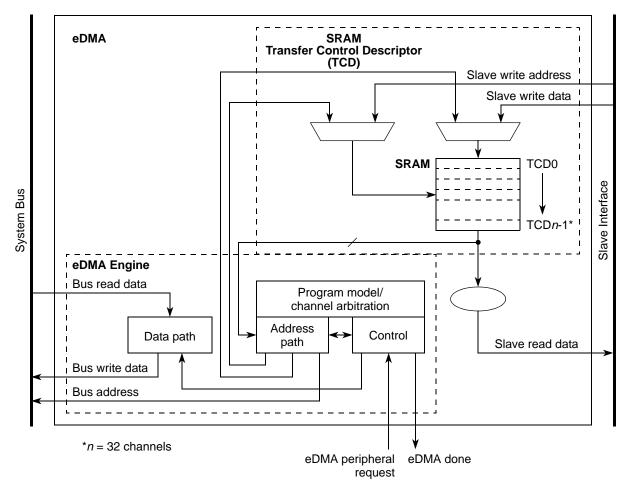

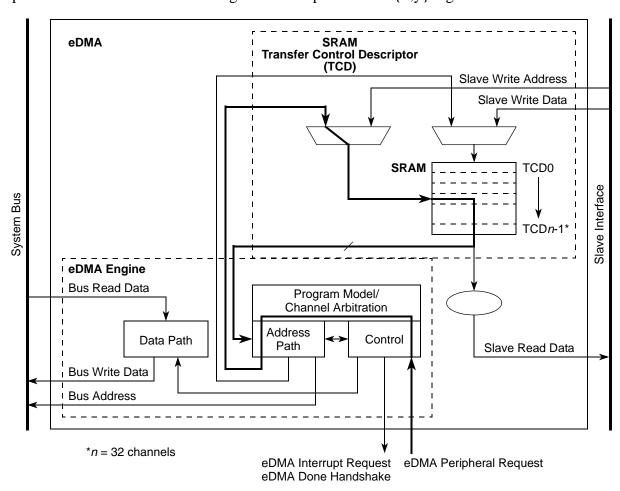

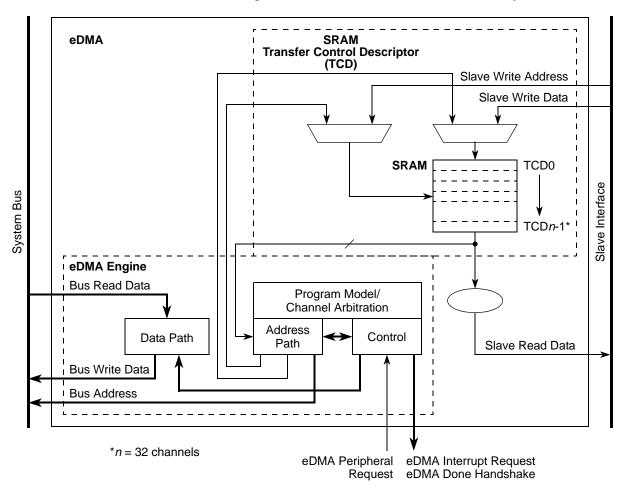

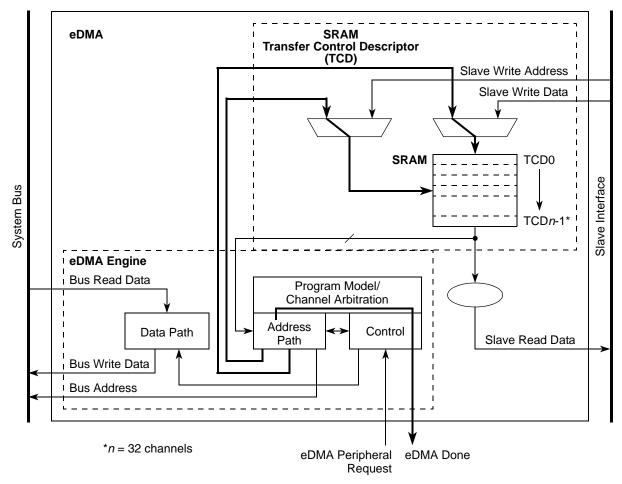

Section 9.3.1, "eDMA Microarchitecture"/ Page 9-29

In the Memory controller sub-bullet, delete the line "The hooks to a BIST controller for the local TCD memory are included in this module".

Table 1. MPC5565RM Rev 1.0 addendum (continued)

|                                                                                 |                                           | ible 1. MPC55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    |                                                              | · · · · · · · · · · · · · · · · · · ·                             |  |  |  |  |

|---------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| Location                                                                        |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                    | Descripti                                                    | on                                                                |  |  |  |  |

| Section 9.2.2.13: eDMA<br>Interrupt Request Register<br>(EDMA_IRQRL)/ Page 9-17 |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | e second paragraph, remove the last line "without the need to perform a read-modify-write ence to the EDMA_IRQRL". |                                                              |                                                                   |  |  |  |  |

| Section 8.3: Initialization and Application Information/Page 8-14               | The men on v Settinon Tran men an essetti | replace the whole section with the following information: the Error Correction Code (ECC) is used to verify the contents of the internal SRAM and from the contents. This is done by generating ECC check bits. Typically ECC check bits are calculated writes and then used on reads to detect and correct errors.  SRAM—Eight ECC check bits for each 64-bit SRAM data doubleword.  Flash—Eight ECC check bits for each 64-bit flash data doubleword.  The Power on Reset (POR), the contents of internal SRAM is random and the correspondence of the contents are unknown. To prevent generating ECC errors during reads, an initializate of the contents of internal SRAM locations. Because the flash module is an envolatile, the ECC check bits are calculated and stored when the flash is programmed. Consequent to the application, the ECC uses the check bits to automatically correct single-termory errors. Multi-bit memory errors are not correctable. If the ECC detects a multi-bit envolved in exception is generated. The type of exception generated by a multi-bit error depends on the tings of the EE and ME in the Machine State Register (MSR), as shown in the following to the error reporting is enabled, as long as its priority is 0, an interrupt request is generated interrupt controller (INTC) even though the INTC request is not serviced. |                                                                                                                    |                                                              |                                                                   |  |  |  |  |

|                                                                                 |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MSR                                                                                                                | EE] and MSR[M                                                | IE] Bit Settings                                                  |  |  |  |  |

|                                                                                 |                                           | Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                    | D                                                            | escription                                                        |  |  |  |  |

|                                                                                 |                                           | EE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 External                                                                                                         | errupt enable.<br>input interrupts dis<br>interrupts enabled |                                                                   |  |  |  |  |

|                                                                                 |                                           | ME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                    |                                                              | isabled. Enters machine check.                                    |  |  |  |  |

|                                                                                 |                                           | on-correctable c<br>-correctable rep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | orting is enal                                                                                                     |                                                              | the following actions, regardless of whether                      |  |  |  |  |

|                                                                                 |                                           | MSR[EE]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MSR[ME]                                                                                                            | Access Type                                                  | Result                                                            |  |  |  |  |

| <u> </u>                                                                        |                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                    |                                                              |                                                                   |  |  |  |  |

|                                                                                 |                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                  | Instruction or data                                          | Enters checkstop state. A reset is required to resume processing. |  |  |  |  |

|                                                                                 |                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                  |                                                              |                                                                   |  |  |  |  |

|                                                                                 |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                    | data Instruction or                                          | required to resume processing.                                    |  |  |  |  |

Table 1. MPC5565RM Rev 1.0 addendum (continued)

| Location                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                              | When the device is in the checkstop state, processing is suspended and cannot resume without a reset. When a debug request is presented to the core while it is in the checkstop state, the core temporarily exits the checkstop state and enters debug mode. When debug mode exits, the core re-enters the checkstop state.  If the external interrupt bit in the MSR is enabled, data or instruction stage interrupts are reported when the ECC errors are a result of CPU accesses, regardless of whether non-correctable                                                                 |

|                                                              | reporting is enabled.  ECC errors generated by other masters (eDMA, etc.) do not generate data or instruction storage exceptions, and the ECSM is used to report these errors. You must initialize the ECSM to enable non-correctable reporting with interrupt generation to detect and report ECC interrupts from the ECSM.                                                                                                                                                                                                                                                                 |

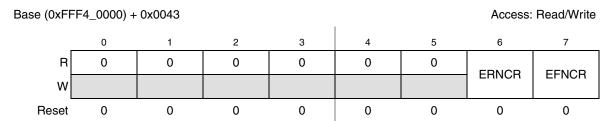

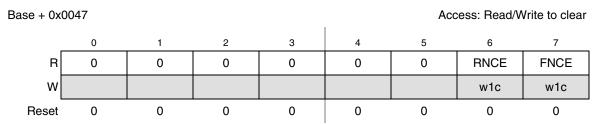

|                                                              | Error reporting details can be independently enabled for flash memory and SRAM. To enable non-correctable error reporting and save the error details for:  • SRAM—set the ERNCR bit in the ECSM Error Configuration Register (ECSM_ECR).  • Flash—set the EFNCR bit in ECSM_ECR.                                                                                                                                                                                                                                                                                                             |

|                                                              | When these bits are set and a non-correctable ECC error occurs, error information is recorded in other ECSM registers and an interrupt request is generated on vector 9 of the interrupt controller (INTC).                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                              | <ul> <li>CPU data access error—Generates data storage exception (IVOR2).</li> <li>CPU instruction access error—Generates instruction storage exception (IVOR3).</li> <li>Vector 9 of INTC enabled—Generates an external exception (IVOR4)</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

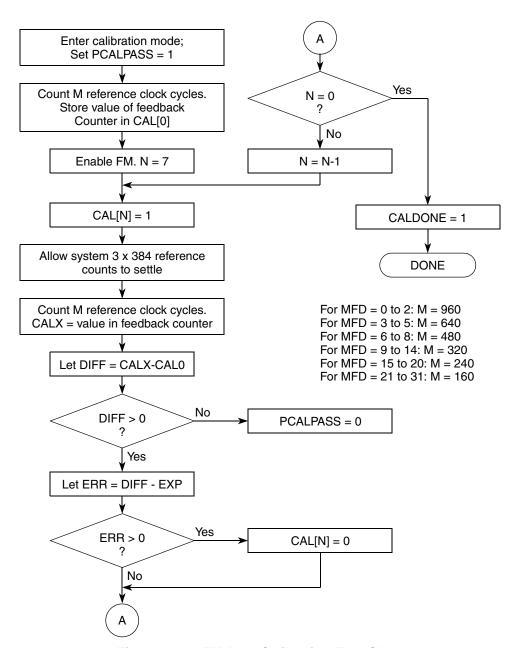

| Section 11.4.3.3, "FM<br>Calibration Routine"/ Page<br>11-29 | Correct the equation at the end of the third paragraph: change value of M from 640 to 480.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

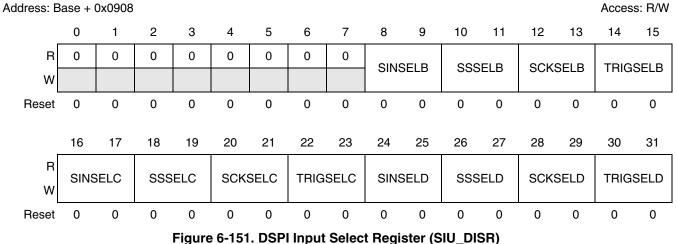

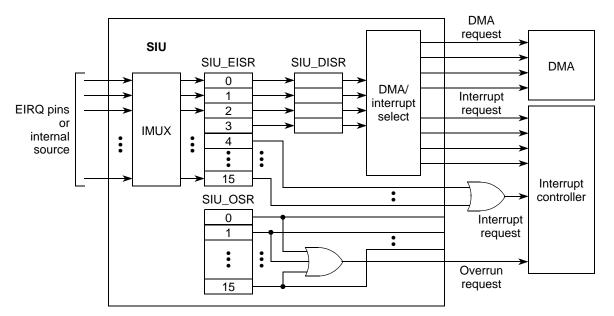

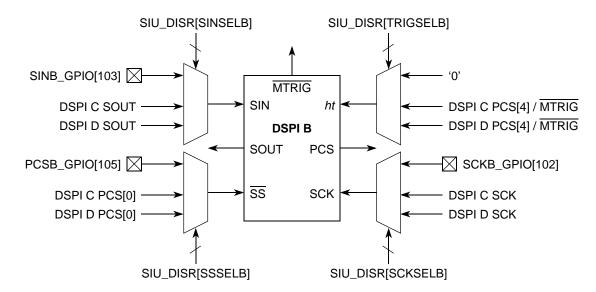

| Table 6-135, "SIU_DISR<br>Field Descriptions"/ Page<br>6-108 | <ul> <li>Bit 14-15–TRIGSELB: Correct the input select description as follows: 00: Replace the term "Invalid value" with "No Trigger" 01: Replace the term "Invalid value" with "No Trigger"</li> <li>Bit 22-23–TRIGSELC: Correct the input select description as follows 00: Replace the term "Invalid value" with "No Trigger" 01: Replace the term "Invalid value" with "No Trigger"</li> <li>Bit 30-31–TRIGSELD: Correct the input select description as follows 00: Replace the term "Invalid value" with "No Trigger" 01: Replace the term "Invalid value" with "No Trigger"</li> </ul> |

Table 1. MPC5565RM Rev 1.0 addendum (continued)

| Location                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |                               | Desc                            | riptio         | า                |                  |           |                |             |                 |      |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|---------------------------------|----------------|------------------|------------------|-----------|----------------|-------------|-----------------|------|

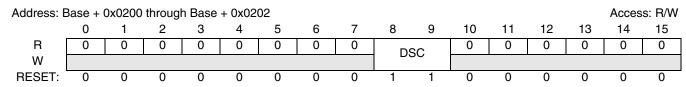

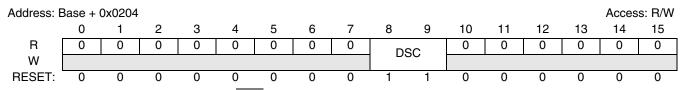

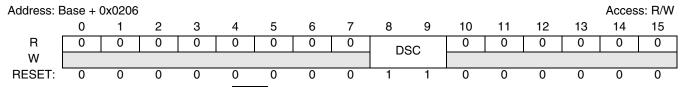

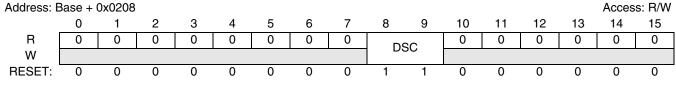

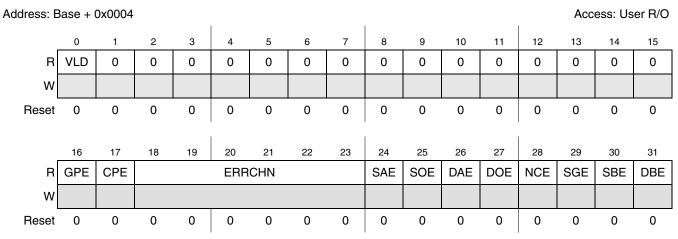

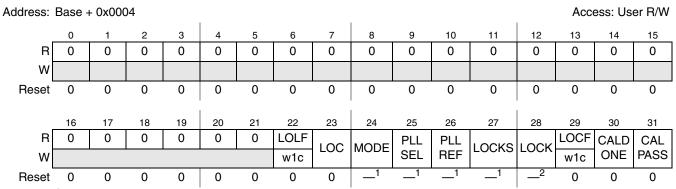

| Figure 11-9, "Synthesizer<br>Status Register<br>(FMPLL_SYNSR)"/Page<br>11-16             | Correct the figure to reflect bits 23:28 and bits 30:31 as read-only.  Addre Base + 0x0004  Access: User                                                                                                                                                                                                                                                                                                                                                       |                               |                               |                                 |                |                  | r R/W            |           |                |             |                 |      |

|                                                                                          | ss:<br>0 1 2 3 4<br>R 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                |                               | 6                             | 7                               | 8              | 9                | 10               | 11        | 12             | 13          | 14              | 15   |

|                                                                                          | W Reset 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 0                           | 0                             | 0                               | 0              | 0                | 0                | 0         | 0              | 0           | 0               | 0    |

|                                                                                          | R 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               | 22<br>LOLF                    | 23<br>LOC                       | 24<br>MO<br>DE | 25<br>PLL<br>SFI | 26<br>PLL<br>REF | LOC<br>KS | 28<br>LOC<br>K | LOC<br>F    | 30<br>CAL<br>DO | PAS  |

|                                                                                          | W Reset 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                              | ) 0                           | w1c                           | 0                               | 1              | 1                | 1                | 1         | 2              | w1c         | NE<br>0         | 0    |

|                                                                                          | 1 Reset state dete 2 Reset state dete Note: "w1c" signific                                                                                                                                                                                                                                                                                                                                                                                                     | ermined<br>ermined<br>es that | d durin<br>d durin<br>this bi | g reset<br>g reset<br>t is clea | i.<br>ared b   | y writi          | ng a 1           |           | SR)            | Ü           | Ü               | Ü    |

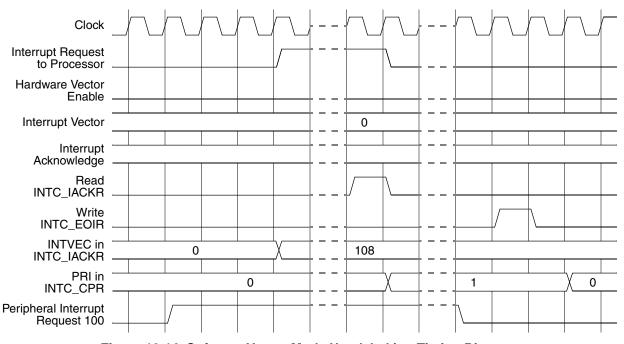

| Section 10.5.5.2, "Ensuring<br>Coherency"/ Page 10-33                                    | dd the following sentence<br>Processor recognition of ir<br>equence."<br>nsert a blank line between                                                                                                                                                                                                                                                                                                                                                            | nterrup                       | ts mus                        | t be en                         | abled          | befor            | e exec           |           |                |             |                 | code |

|                                                                                          | etResource:<br>aise PRI<br>bar<br>sync                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |                               |                                 |                |                  |                  |           |                | , , , , , , |                 |      |

|                                                                                          | eleaseResource:<br>bar<br>ower PRI                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                               |                                 |                |                  |                  |           |                |             |                 |      |

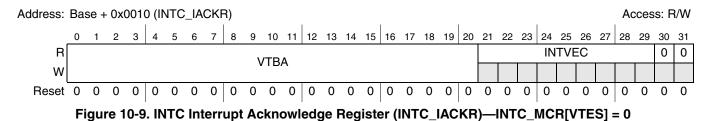

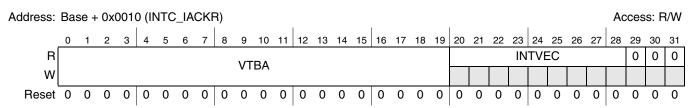

| Section 10.3.1.3, "INTC<br>Interrupt Acknowledge<br>Register<br>(INTC_IACKR)"/Page 10-11 | temove the first paragraph<br>The INTC_IACKR must no<br>uture compatibility, the TLE                                                                                                                                                                                                                                                                                                                                                                           | t be re                       | ad spe                        | culativ                         |                |                  |                  |           |                |             |                 |      |

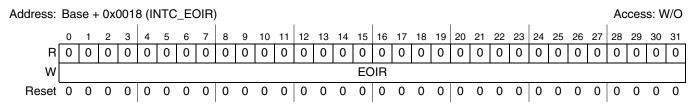

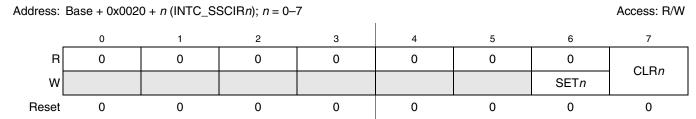

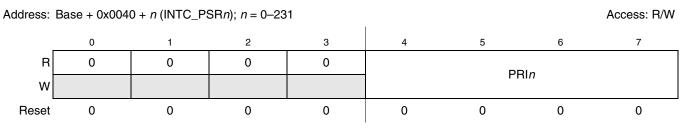

| Table 10-3. INTC Memory<br>Map/Page 10-8                                                 | Add the following note at the end of this table:  Note: To ensure compatibility with all PowerPC processors, the TLB entry covering the INTC memory map must be configured as guarded, both in software and hardware vector modes.  In software vector mode, the INTC_IACKR must not be read speculatively.  In hardware vector mode, guarded writes to the INTC_CPR or INTC_EOIR complete before the interrupt acknowledge signal from the processor asserts. |                               |                               |                                 |                |                  |                  |           |                |             |                 |      |

Table 1. MPC5565RM Rev 1.0 addendum (continued)